Surface-Trap-Induced Hysteresis in an InAs Nanowire FET — a Density-Gradient Analysis

Application ID: 97361

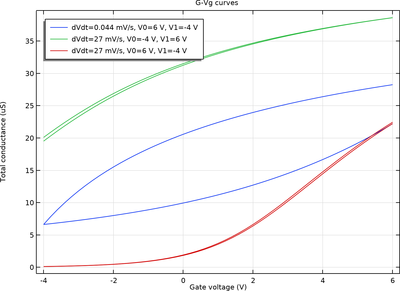

This tutorial analyzes the hysteresis of the conductance-gate-voltage (G-Vg) curves of an InAs nanowire FET, using the density-gradient theory to add the effect of quantum confinement to the conventional drift-diffusion formulation, without a large increase of computational costs. The hysteresis is caused by the dynamic charging effects of fast and slow semiconductor-oxide interface traps of continuous energy distributions and of both donor and acceptor types. The capture probability is modeled as thermally activated with a barrier height that varies with the trap energy level. The qualitative behavior and the order of magnitude of the computed G-Vg curves under various voltage ramping conditions agree well with simulation and experiment results found in the literature.

Dieses Beispiel veranschaulicht Anwendungen diesen Typs, die mit den folgenden Produkten erstellt wurden:

Allerdings können zusätzliche Produkte erforderlich sein, um es vollständig zu definieren und zu modellieren. Weiterhin kann dieses Beispiel auch mit Komponenten aus den folgenden Produktkombinationen definiert und modelliert werden:

Die Kombination von COMSOL® Produkten, die für die Modellierung Ihrer Anwendung erforderlich ist, hängt von verschiedenen Faktoren ab und kann Randbedingungen, Materialeigenschaften, Physik-Interfaces und Bauteilbibliotheken umfassen. Bestimmte Funktionen können von mehreren Produkten gemeinsam genutzt werden. Um die richtige Produktkombination für Ihre Modellierungsanforderungen zu ermitteln, lesen Sie die Spezifikationstabelle und nutzen Sie eine kostenlose Evaluierungslizenz. Die COMSOL Vertriebs- und Support-Teams stehen Ihnen für alle Fragen zur Verfügung, die Sie diesbezüglich haben.