Electrical Stress in High Voltage Capacitor Units

As modern electrical power networks grow to reduce costs to consumers, improve security of supply, and make better use of renewable energy, power electronic interfaces are set to become increasingly commonplace by allowing controllability, diversity in supply and demand, and the asynchronous connections necessary for renewable resources. Power electronic converter interfaces use capacitor banks to support reactive power and direct current voltage, and as components of tuned filtering arrangements.

For such applications, resilience to electrical field stresses is critical to capacitor unit design: electrical stresses within capacitor assets can degrade insulation and cultivate incipient faults [1]. Left unchecked, a developing fault can gradually lead to insulation breakdown and reduce the overall capacitance of a unit or bank, which can in turn lead to cascading failure as greater voltages are shared across a reduced asset reactance [2].

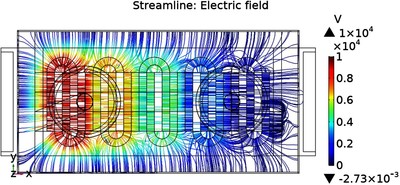

COMSOL Multiphysics'® AC/DC Module is employed in this study to emulate electrical field stresses throughout a simplified capacitor unit. Regions of high electrical field stress are highlighted using an electrostatics boundary condition for consideration in capacitor design engineering. Their implications for fault development and progression in capacitor banks are noted.

While this study makes use of a simplistic capacitor model geometry of static size, approximates a homogenous dielectric, and ignores sources of noise inherent to real applications, it could offer some limited insight into physical influences within enclosed assets, which are at present adopting an increasingly pervasive role in electrical infrastructure, and is configurable such that other capacitor designs can be studied with relative ease.

An awareness of asset failure modes is necessary for engineering design and can inform decision-making for maintenance activities in operational contexts.

References

[1] C. W. Reed, S. W. Chichanowski, ``The fundamentals of aging in HV polymer-film capacitors'', IEEE Transactions on Dielectrics and Electrical Insulation, Vol. 1, No. 5, October 1994.

[2] M. Ellis, D. J. Meisner, M. Thakur, ``Innovative protection schemes for H configuration fuseless grounded shunt capacitor banks'', 65th Annual Conference for Protective Relay Engineers, 2012.

Herunterladen

- CONFS.Paper.pMax7.2019-08-23.V26.pdf - 0.8MB

- CONFS.COMSOL.2019-08-23.V11.pptx - 7.39MB